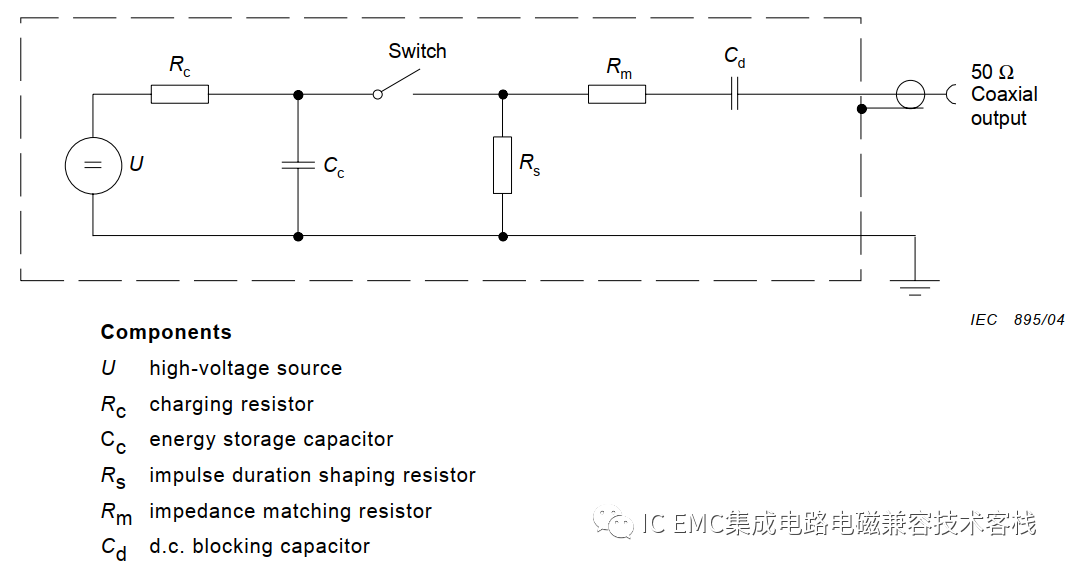

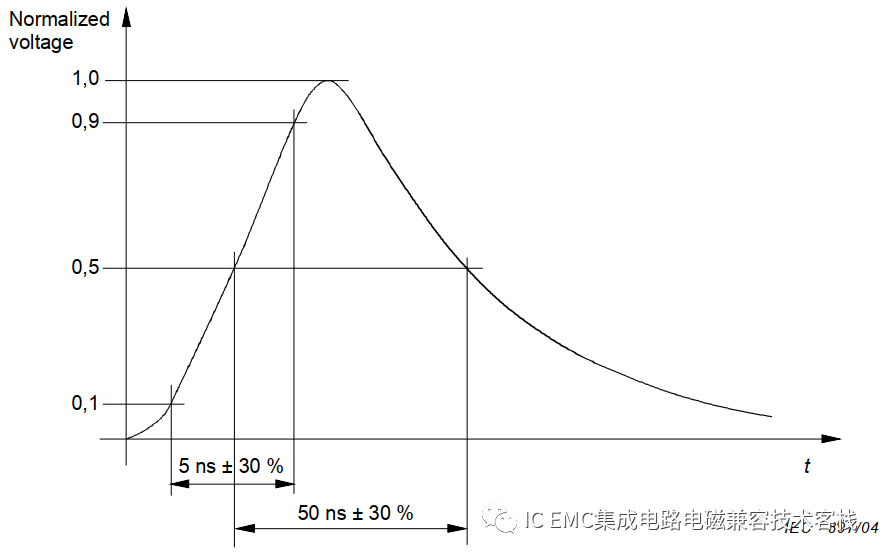

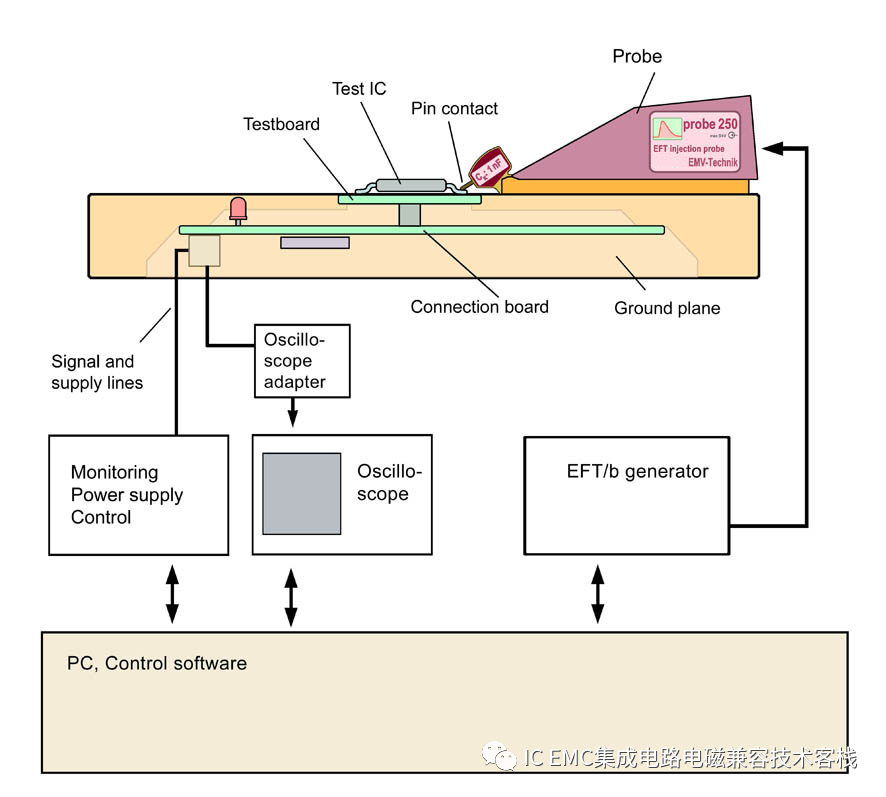

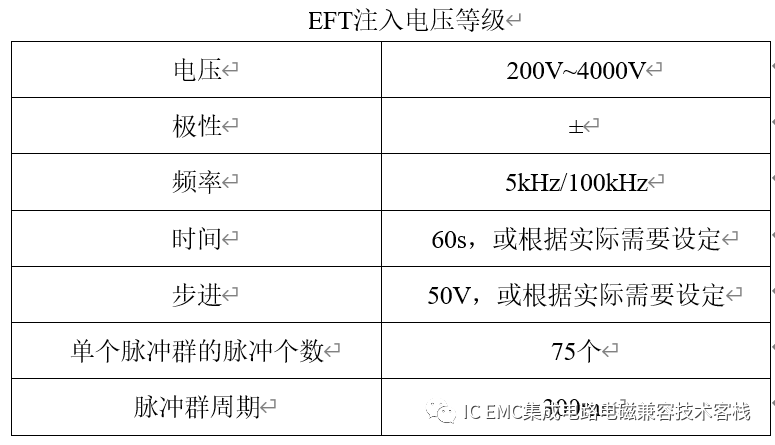

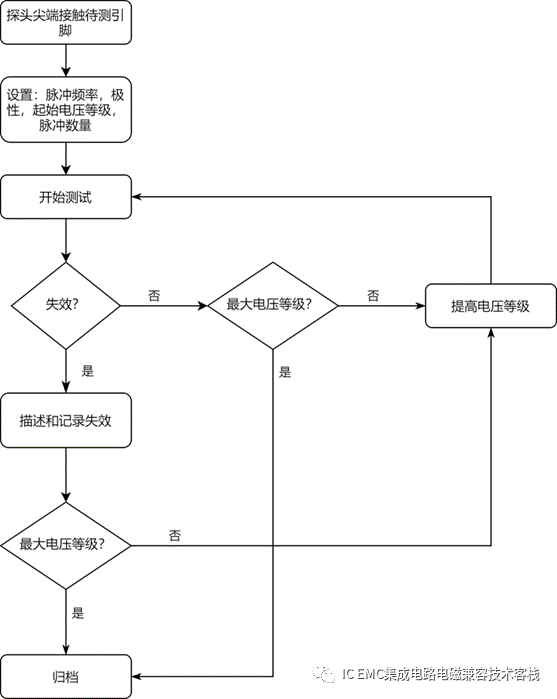

截至发稿,上一篇文章 IC带电ESD测试方法介绍 阅读量已经突破800,创了本公众号的历史浏览记录,看得出来大家对IC ESD的关注度和熟悉度十分高,毕竟IC设计中必不可少的模块——IO保护电路的核心作用就是ESD防护,其实IO保护电路还有另一个作用就是EFT防护,本文介绍的EFT测试也就是用于评估该防护的等级,下面介绍IC EFT测试方法,该方法对应的国际测试标准为IEC62215-3。EFT干扰源波形: EFT(电快速瞬变脉冲群)干扰源不同于ESD的一大特征就是ESD是单个脉冲注入,而EFT是一组脉冲,称为脉冲群,其波形模型依据系统级测试标准IEC61000-4-4,模型的等效电路、典型波形(单个脉冲和脉冲群)和波形参数如下,这些参数也是市面上EFT脉冲发生器设备需要满足的技术指标。     EFT干扰源设备: 目前做IC EFT测试,采用的干扰源设备主要由EFT发生器+注入探头组成。EFT发生器的个头比较大,属于高压设备,需要特别注意安全性操作,实物参考如下:  注入探头主要是为了适配IC测试环境,满足标准要求添加不同的耦合电容,成熟的方案实物如下:  EFT测试配置: 通用的测试布置主要包括EFT发生器、注入耦合探头、接地铜盘夹具、监测设备和PC控制电脑。   测试流程: 同ESD的流程一致,特别地,EFT测试单次测试等待的时间是秒级,相对而言用时更长。  以上整个内容与ESD测试是十分相似的,测试就是这样,比较机械化(枯燥,哈哈),其实IC测试的难点不在测试,而在测试方案的确定,因为IC的种类太多了,比如,带CPU的和不带CPU的(是否需要跑代码),测试时芯片的工作状态的定义、测试的失效判据的定义,都取决于芯片的设计参数和功能参数等等,因此需要与IC设计者保持密切联系,故而最早研究IC EMC测试的都是IC设计的大厂,尤其是IDM厂商,他们有条件可以完成设计、仿真、测试和优化迭代整套流程。稍微扯远了。。。 |